### YETI: A GRADUALLY EXTENSIBLE TRACE INTERPRETER

by

Mathew Zaleski

A thesis submitted in conformity with the requirements for the degree of Doctor of Philosophy Graduate Department of Computer Science University of Toronto

Copyright © 2007 by Mathew Zaleski

### Abstract

YETI: a graduallY Extensible Trace Interpreter

Mathew Zaleski Doctor of Philosophy Graduate Department of Computer Science University of Toronto 2007

The implementation of new programming languages benefits from interpretation because it is simple, flexible and portable. The only downside is speed of execution, as there remains a large performance gap between even efficient interpreters and systems that include a just-intime (JIT) compiler. Augmenting an interpreter with a JIT, however, is not a small task. Today, Java JITs are typically method-based. To compile whole methods, the JIT must re-implement much functionality already provided by the interpreter, leading to a "big bang" development effort before the JIT can be deployed. Adding a JIT to an interpreter would be easier if we could more gradually shift from dispatching virtual instructions bodies implemented for the interpreter to running instructions compiled into native code by the JIT.

We show that virtual instructions implemented as lightweight callable routines can form the basis for a very efficient interpreter. Our new technique, interpreted traces, identifies hot paths, or traces, as a virtual program is interpreted. By exploiting the way traces predict branch destinations our technique markedly reduces branch mispredictions caused by dispatch. Interpreted traces are a high-performance technique, running about 25% faster than direct threading.

We show that interpreted traces are a good starting point for a trace-based JIT. We extend our interpreter so traces may contain a mixture of compiled code for some virtual instructions and calls to virtual instruction bodies for others. By compiling about 50 integer and object virtual instructions to machine code we improve performance by about 30% over interpreted traces, running about twice as fast as the direct threaded system with which we started.

### Acknowledgements

My supervisor, Angela Demke Brown uncomplainingly drew the short straw when she was handed me, a middle-aged electrical engineer turned businessman, as her first doctoral student. Overcoming many obstacles she has taught me the subtle craft of systems research.

I thank my advisory committee of Michael Stumm, David Wortman and Tarek Abdelrahman for their input and guidance on our research. Special thanks are also due to Kevin Stoodley of IBM, without whose insight this research would not have been possible.

My family must at some level be to blame for my decision to interrupt (even jeopardize?) a reasonably successful and entirely enjoyable career to spend the last several years retraining as a researcher. Leonard, my father, would have been pleased had I written this dissertation twenty years ago. If I had, he would have been alive to read it. My mother, Irma, has written several books on religion while I completed my studies. Her love of knowledge, and the process of writing it down, has been impetus for my less ethereal work. My father-in-law, Harry Eastman, advised me throughout the process of returning to school. I doubt I would have had the nerve to carry it through without his support. I wish he were still with us to pull his academic hood out of mothballs and see me over the threshold one more time.

My wife, Harriet Eastman, has been a paragon of support and patience while I enjoyed the thrills and chills of the PhD program. Without her love and encouragement I would have given up long ago. Our children, Sam and Jacob, while occasionally benefiting from my flexible hours, were more often called upon to be good sports when the flexibility simply meant I worked all the time.

## Contents

| 1 | Intro | roduction 1                |                                                                    |    |  |

|---|-------|----------------------------|--------------------------------------------------------------------|----|--|

|   | 1.1   | Challe                     | nges of Method-based JIT Compilation                               | 3  |  |

|   | 1.2   | Challe                     | nges of Efficient Interpretation                                   | 4  |  |

|   | 1.3   | What V                     | We Need                                                            | 4  |  |

|   | 1.4   | Overview of Our Solution   |                                                                    |    |  |

|   | 1.5   | Thesis                     | Statement                                                          | 8  |  |

|   | 1.6   | Contri                     | butions                                                            | 8  |  |

|   | 1.7   | Outline of Thesis          |                                                                    |    |  |

| 2 | Back  | kground                    | 1                                                                  | 13 |  |

|   | 2.1   | High L                     | Level Language Virtual Machine                                     | 13 |  |

|   |       | 2.1.1                      | Overview of a Virtual Program                                      | 15 |  |

|   |       | 2.1.2                      | Interpretation                                                     | 16 |  |

|   |       | 2.1.3                      | Early Just in Time Compilers                                       | 17 |  |

|   | 2.2   | Challe                     | nges to HLL VM Performance                                         | 18 |  |

|   |       | 2.2.1                      | Polymorphism and the Implications of Object-oriented Programming . | 19 |  |

|   |       | 2.2.2                      | Late binding                                                       | 22 |  |

|   | 2.3   | Early Dynamic Optimization |                                                                    | 23 |  |

|   |       | 2.3.1                      | Manual Dynamic Optimization                                        | 23 |  |

|   |       | 2.3.2                      | Application specific dynamic compilation                           | 23 |  |

|   |      | 2.3.3                                | Dynamic Compilation of Manually Identified Static Regions | 24 |

|---|------|--------------------------------------|-----------------------------------------------------------|----|

|   | 2.4  | Dynamic Object-oriented optimization |                                                           |    |

|   |      | 2.4.1                                | Finding the destination of a polymorphic callsite         | 25 |

|   |      | 2.4.2                                | Smalltalk and Self                                        | 27 |

|   |      | 2.4.3                                | Java JIT as Dynamic Optimizer                             | 29 |

|   |      | 2.4.4                                | JIT Compiling Partial Methods                             | 30 |

|   | 2.5  | Traces                               |                                                           | 31 |

|   | 2.6  | Hotpat                               | h                                                         | 33 |

|   | 2.7  | Chapte                               | er Summary                                                | 34 |

| 3 | Disp | atch Te                              | chniques                                                  | 35 |

|   | 3.1  | Switch                               | Dispatch                                                  | 36 |

|   | 3.2  | Direct                               | Call Threading                                            | 38 |

|   | 3.3  | Direct                               | Threading                                                 | 38 |

|   | 3.4  | Dynam                                | nic Hardware Branch Prediction                            | 40 |

|   | 3.5  | The Co                               | ontext Problem                                            | 41 |

|   | 3.6  | Subroutine Threading                 |                                                           |    |

|   | 3.7  | Optimizing Dispatch                  |                                                           |    |

|   |      | 3.7.1                                | Superinstructions                                         | 44 |

|   |      | 3.7.2                                | Selective Inlining                                        | 44 |

|   |      | 3.7.3                                | Replication                                               | 46 |

|   | 3.8  | Chapte                               | er Summary                                                | 46 |

| 4 | Desi | gn and                               | Implementation of Efficient Interpretation                | 47 |

|   | 4.1  | Unders                               | standing Branches                                         | 49 |

|   | 4.2  | Handli                               | ng Linear Dispatch                                        | 51 |

|   | 4.3  | Handli                               | ng Virtual Branches                                       | 52 |

|   | 4.4  | Handli                               | ng Virtual Call and Return                                | 56 |

|                                    | 4.5                             | Chapte                   | er Summary                                   | 58 |  |

|------------------------------------|---------------------------------|--------------------------|----------------------------------------------|----|--|

| 5                                  | Evaluation of Context Threading |                          |                                              |    |  |

|                                    | 5.1                             | Experi                   | mental Set-up                                | 62 |  |

|                                    |                                 | 5.1.1                    | Virtual Machines and Benchmarks              | 62 |  |

|                                    |                                 | 5.1.2                    | Performance and Pipeline Hazard Measurements | 64 |  |

|                                    | 5.2                             | Interpr                  | reting the data                              | 65 |  |

|                                    |                                 | 5.2.1                    | Effect on Pipeline Branch Hazards            | 69 |  |

|                                    |                                 | 5.2.2                    | Performance                                  | 70 |  |

|                                    | 5.3                             | Inlinin                  | g                                            | 74 |  |

|                                    | 5.4                             | Limita                   | tions of Context Threading                   | 76 |  |

|                                    |                                 | 5.4.1                    | Heavyweight Virtual Instruction Bodies       | 76 |  |

|                                    |                                 | 5.4.2                    | Context Threading and Profiling              | 77 |  |

|                                    |                                 | 5.4.3                    | Development using SableVM                    | 78 |  |

|                                    | 5.5                             | Chapte                   | er Summary                                   | 79 |  |

| 6                                  | Desi                            | gn and                   | Implementation of YETI                       | 81 |  |

| 6.1 Structure and Overview of Yeti |                                 | are and Overview of Yeti | 82                                           |    |  |

|                                    | 6.2                             | Regior                   | n Selection                                  | 86 |  |

|                                    |                                 | 6.2.1                    | Initiating Region Discovery                  | 86 |  |

|                                    |                                 | 6.2.2                    | Linear Block Detection                       | 87 |  |

|                                    |                                 | 6.2.3                    | Trace Selection                              | 89 |  |

|                                    | 6.3                             | Trace                    | Exit Runtime                                 | 90 |  |

|                                    |                                 | 6.3.1                    | Trace Linking                                | 92 |  |

|                                    | 6.4                             | Genera                   | ating code for traces                        | 93 |  |

|                                    |                                 | 6.4.1                    | Interpreted Traces                           | 94 |  |

|                                    |                                 | 6.4.2                    | JIT Compiled Traces                          | 95 |  |

|                                    |                                 | 6.4.3                    | Trace Optimization                           | 99 |  |

|    | 6.5             | Other implementation details                         |  |  |

|----|-----------------|------------------------------------------------------|--|--|

|    | 6.6             | Chapter Summary                                      |  |  |

| 7  | Eval            | aluation of Yeti                                     |  |  |

|    | 7.1             | Experimental Set-up                                  |  |  |

|    | 7.2             | Effect of region shape on dispatch                   |  |  |

|    | 7.3             | Effect of region shape on performance                |  |  |

|    | 7.4             | Early Pentium Results                                |  |  |

|    | 7.5             | Identification of Stall Cycles                       |  |  |

|    |                 | 7.5.1 Identifying Causes of Stall Cycles             |  |  |

|    |                 | 7.5.2 Stall Cycle results                            |  |  |

|    |                 | 7.5.3 Trends                                         |  |  |

|    | 7.6             | Chapter Summary                                      |  |  |

| 8  | Con             | lusions and Future Work 133                          |  |  |

|    | 8.1             | Conclusions and Lessons Learned                      |  |  |

|    | 8.2 Future work |                                                      |  |  |

|    |                 | 8.2.1 Virtual instruction bodies as nested functions |  |  |

|    |                 | 8.2.2 Extension to Runtime Typed Languages           |  |  |

|    |                 | 8.2.3 New shapes of region body                      |  |  |

|    |                 | 8.2.4 Vision for new language implementation         |  |  |

|    | 8.3             | Summary                                              |  |  |

| Bi | bliogr          | aphy 141                                             |  |  |

## **List of Tables**

| 5.1 | Description of OCaml benchmarks. Raw elapsed time and branch hazard data             |    |

|-----|--------------------------------------------------------------------------------------|----|

|     | for direct-threaded runs.                                                            | 63 |

| 5.2 | Description of SPECjvm98 Java benchmarks. Raw elapsed time and branch                |    |

|     | hazard data for direct-threaded runs                                                 | 64 |

| 5.3 | (a) Guide to Technique description                                                   | 66 |

| 5.4 | Detailed comparison of selective inlining (SABLEVM) vs SUB+BI+AR and                 |    |

|     | TINY. Numbers are elapsed time relative to direct threading. $\triangle context$ is  |    |

|     | the the difference between selective inlining and SUB+BI+AR. $\triangle tiny$ is the |    |

|     | difference between selective inlining and TINY (the combination of context           |    |

|     | threading and tiny inlining)                                                         | 76 |

| 7.1 | SPECjvm98 benchmarks including elapsed time for baseline JamVM (i.e.,                |    |

|     | without any of our modifications), Yeti and Sun HotSpot                              | 07 |

| 7.2 | Guide to labels which appear on figures and references to technique descriptions.1   | 07 |

| 7.3 | GPUL categories                                                                      | 24 |

# **List of Figures**

| 2.1 | Example Java Virtual Program showing source (on the left) and Java virtual         |    |

|-----|------------------------------------------------------------------------------------|----|

|     | instructions, or bytecodes, on the right.                                          | 15 |

| 2.2 | Example of Java method containing a polymorphic callsite                           | 20 |

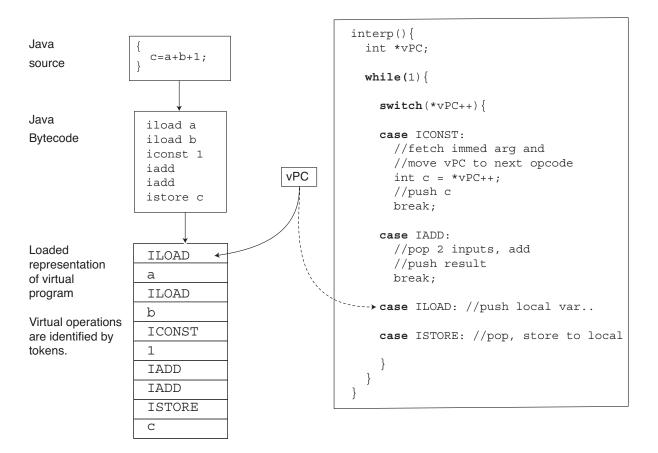

| 3.1 | A switch interpreter loads each virtual instruction as a virtual opcode, or token, |    |

|     | corresponding to the case of the switch statement that implements it. Virtual      |    |

|     | instructions that take immediate operands, like iconst, must fetch them from       |    |

|     | the vPC and adjust the vPC past the operand. Virtual instructions which do not     |    |

|     | need operands, like iadd, do not need to adjust the vPC                            | 37 |

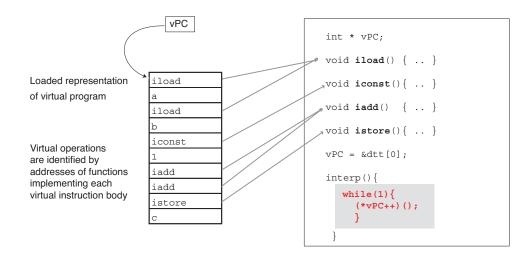

| 3.2 | A direct call-threaded interpreter packages each virtual instruction body as a     |    |

|     | function. The shaded box highlights the dispatch loop showing how virtual          |    |

|     | instructions are dispatched through a function pointer. Direct call threading      |    |

|     | requires the loaded representation of the program to point to the address of the   |    |

|     | function implementing each virtual instruction.                                    | 39 |

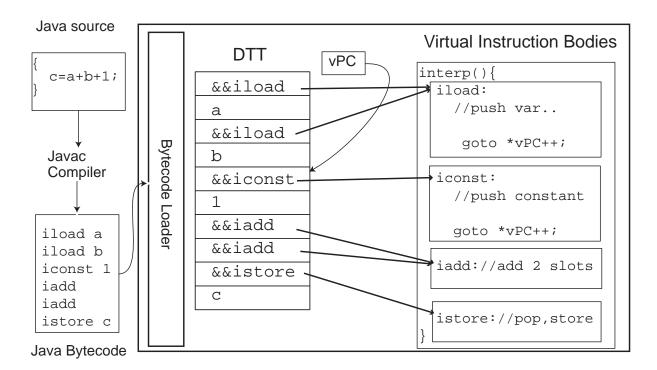

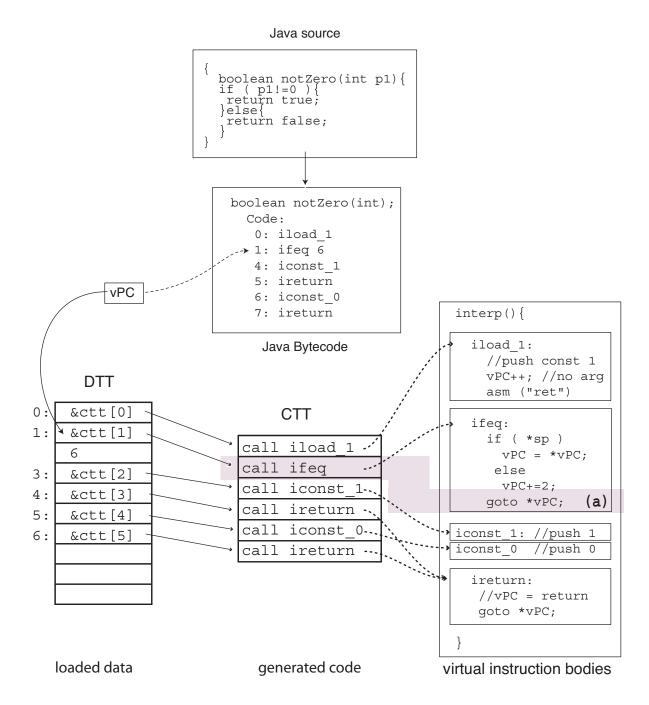

| 3.3 | Direct-threaded Interpreter showing how Java Source code compiled to Java          |    |

|     | bytecode is loaded into the Direct Threading Table (DTT). The virtual instruc-     |    |

|     | tion bodies are written in a single C function, each identified by a separate      |    |

|     | label. The double-ampersand (&&) shown in the DTT is gcc syntax for the            |    |

|     | address of a label.                                                                | 39 |

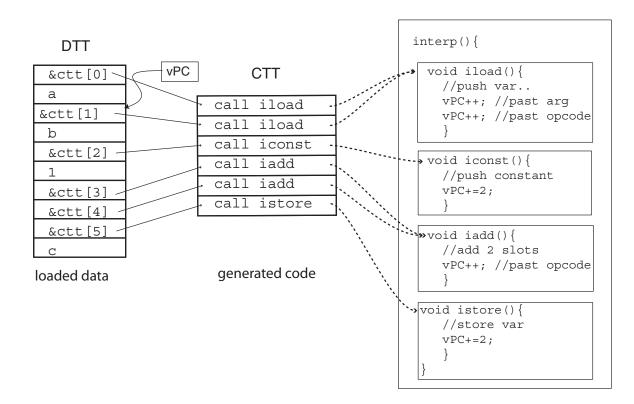

- 4.1 Subroutine Threaded Interpreter showing how the CTT contains one generated direct call instruction for each virtual instruction and how the first entry in the DTT corresponding to each virtual instruction points to generated code to dispatch it. Callable bodies are shown here as nested functions for illustration only. All maintenance of the vPC must be done in the bodies. Hence even virtual instructions that take no arguments, like iadd, must bump vPC past the virtual instructions, like iload, that take an argument must bump vPC past the argument as well.

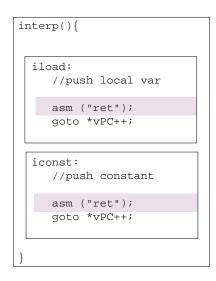

- 4.2 Direct threaded bodies retrofitted as callable routines by inserting inline assembler return instructions. This example is for Pentium 4 and hence ends each body with a ret instruction. The asm statement is an extension to the C language, inline assembler, provided by gcc and many other compilers. . . . . 51

50

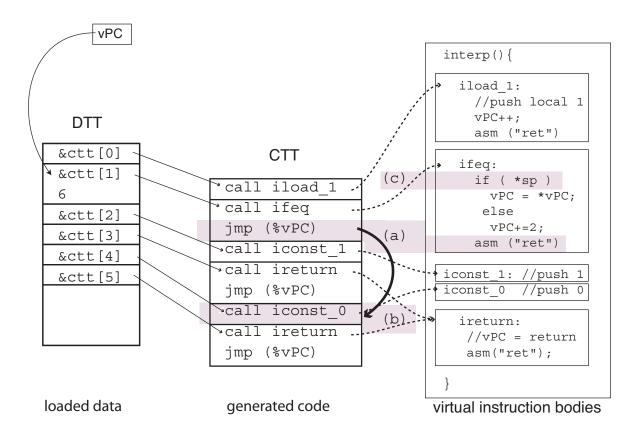

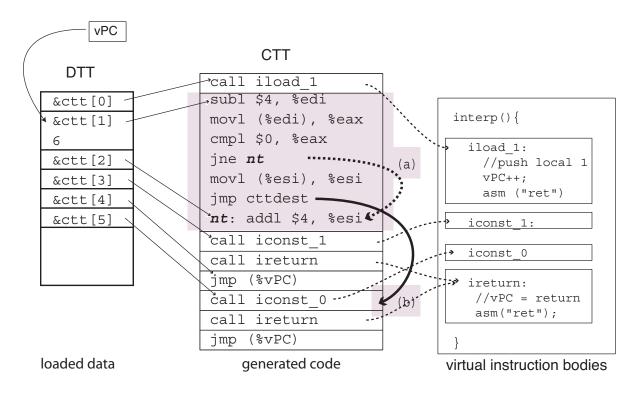

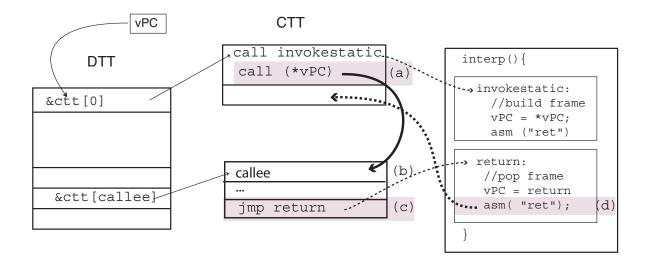

| 4.5 | Context-threaded VM Interpreter: Branch Inlining. The dashed arrow (a) il-            |    |

|-----|---------------------------------------------------------------------------------------|----|

|     | lustrates the inlined conditional branch instruction, now fully exposed to the        |    |

|     | branch prediction hardware, and the heavy arrow (b) illustrates a direct branch       |    |

|     | implementing the not taken path. The generated code (shaded) assumes the              |    |

|     | vPC is in register $esi$ and the Java expression stack pointer is in register $edi$ . |    |

|     | (In reality, we dedicate registers in the way shown for SableVM on the Pow-           |    |

|     | erPC only. On the Pentium4, due to lack of registers, the $vPC$ is actually stored    |    |

|     | on the stack. )                                                                       | 56 |

| 4.6 | Context Threading Apply-Return Inlining on Pentium. The generated code                |    |

|     | calls the invokestatic virtual instruction body but jumps (instruction at             |    |

|     | (c) is a jmp) to the return body                                                      | 57 |

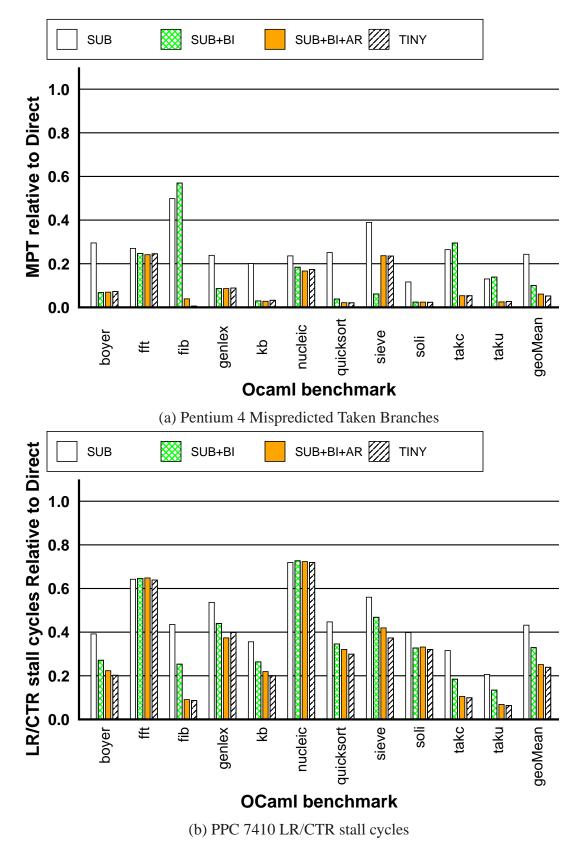

| 5.1 | OCaml Dinalina Hazarda Dalativa ta Diraat Thraading                                   | 67 |

|     | OCaml Pipeline Hazards Relative to Direct Threading                                   |    |

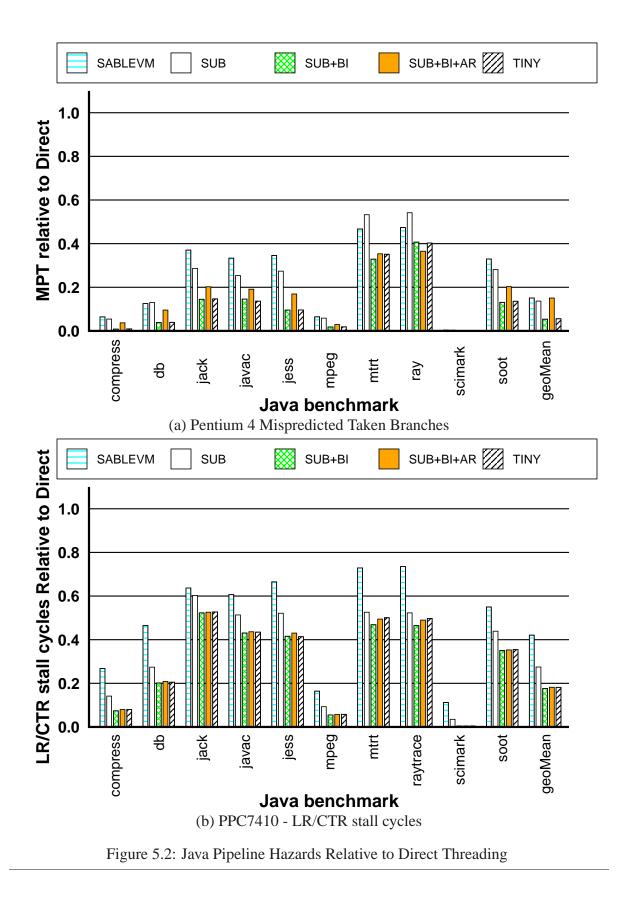

| 5.2 | Java Pipeline Hazards Relative to Direct Threading                                    | 68 |

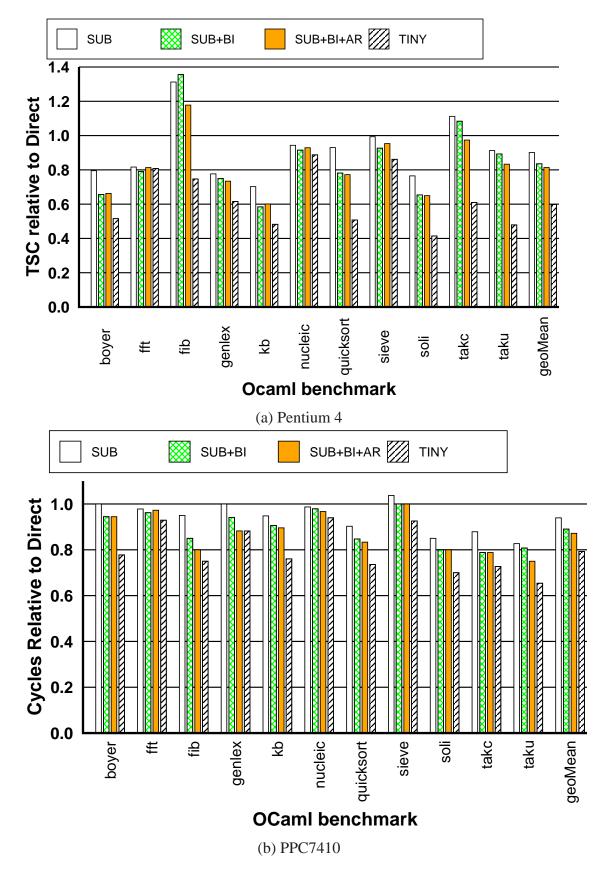

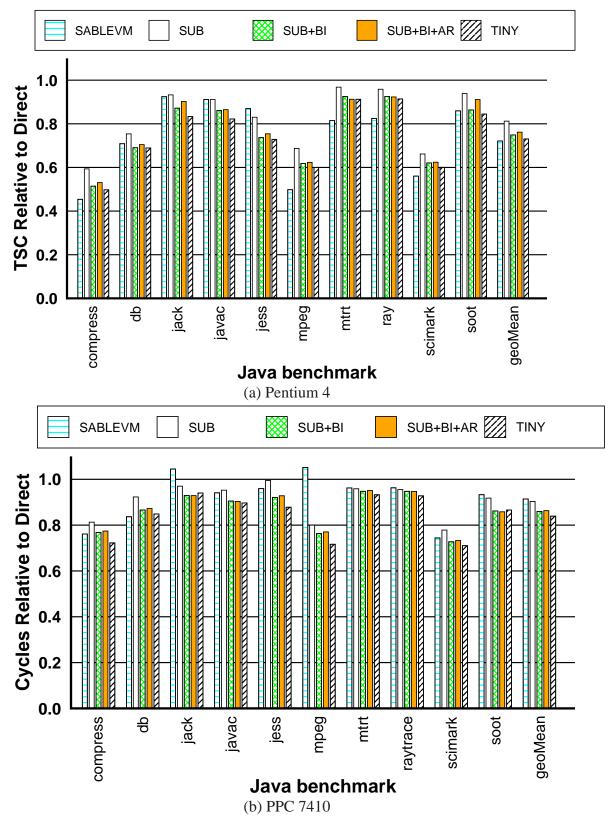

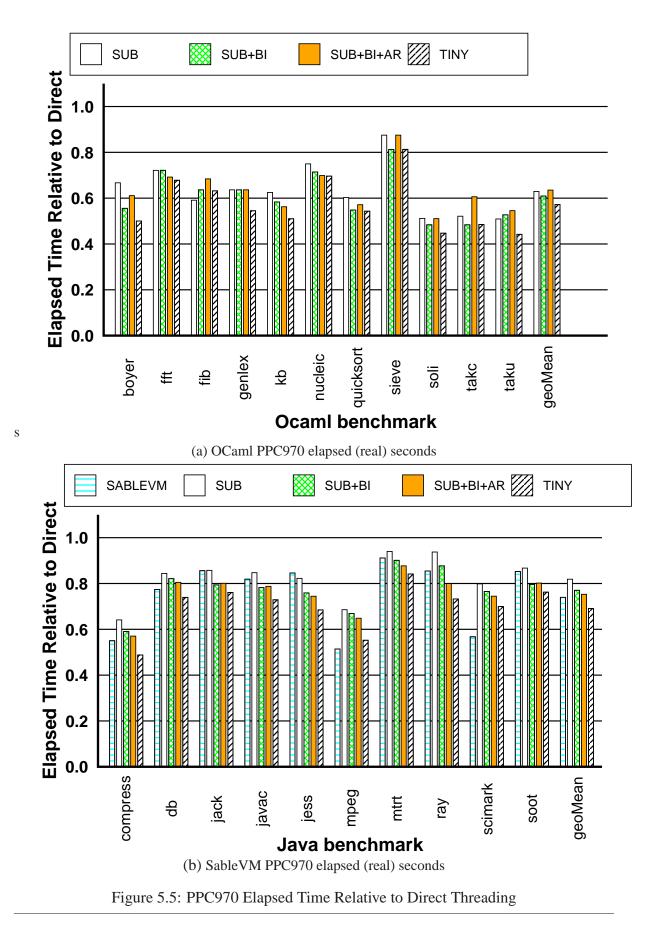

| 5.3 | OCaml Elapsed Time Relative to Direct Threading                                       | 71 |

| 5.4 | SableVM Elapsed Time Relative to Direct Threading                                     | 72 |

| 5.5 | PPC970 Elapsed Time Relative to Direct Threading                                      | 73 |

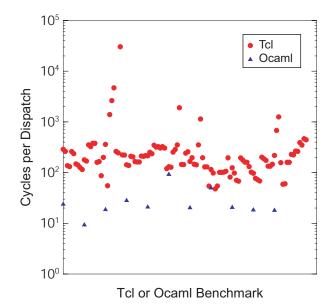

| 5.6 | Reproduction of [77, Figure 1] showing cycles run per virtual instructions dis-       |    |

|     | patched for various Tcl and OCaml benchmarks                                          | 77 |

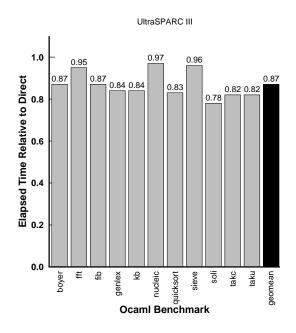

| 5.7 | Elapsed time of subroutine threading relative to direct threading for OCaml on        |    |

|     | UltraSPARC III.                                                                       | 78 |

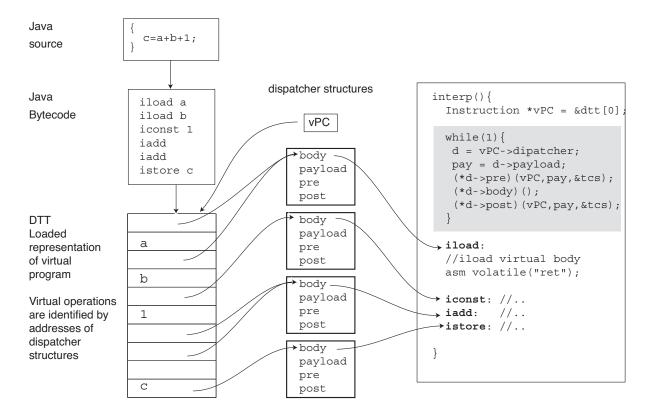

| 6.1 | Virtual program loaded into Yeti showing how dispatcher structures are ini-           |    |

|     | tially shared between all instances of a virtual instruction. The dispatch loop,      |    |

|     | shaded, is similar the dispatch loop of direct call threading except that another     |    |

|     | level of indirection, through the the dispatcher structure, has been added. Pro-      |    |

|     | filing instrumentation is called before and after the dispatch of the body            | 85 |

|     | - 1 /                                                                                 |    |

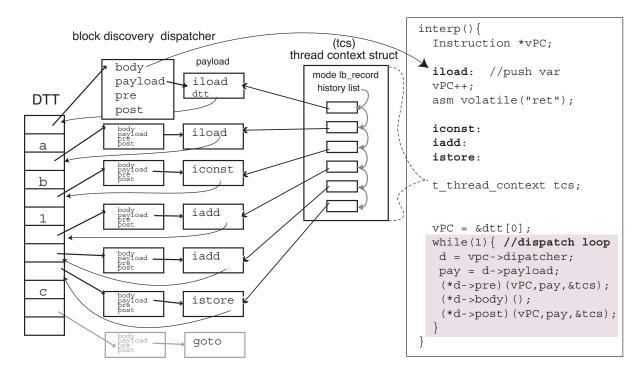

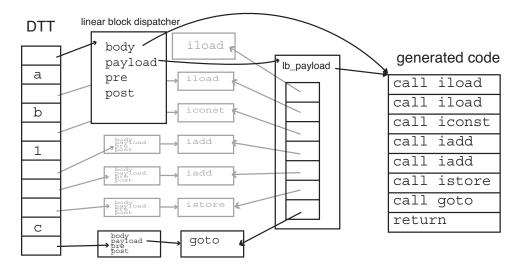

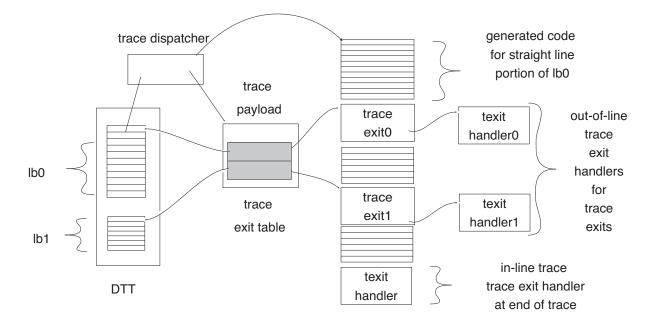

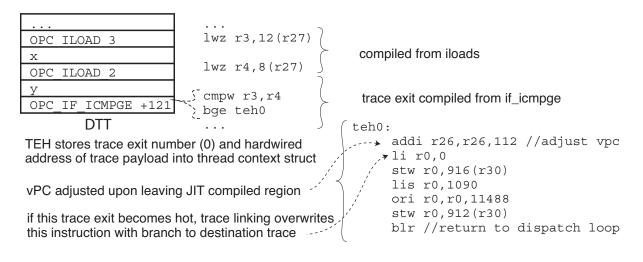

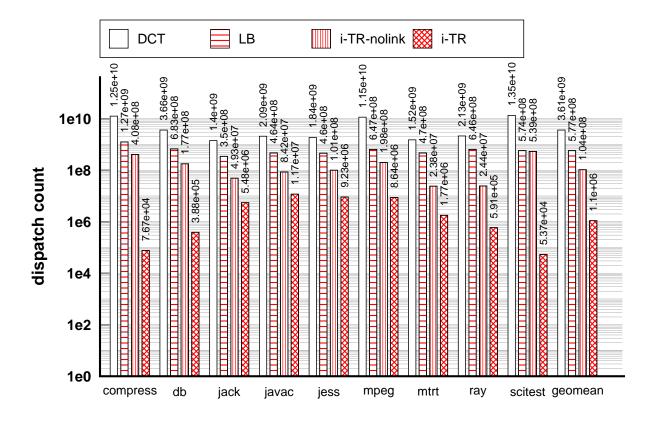

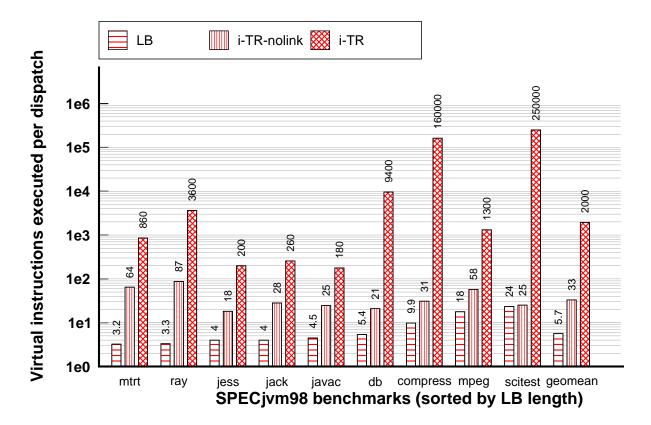

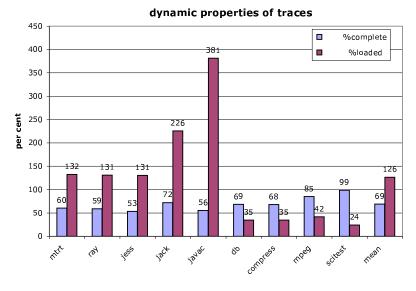

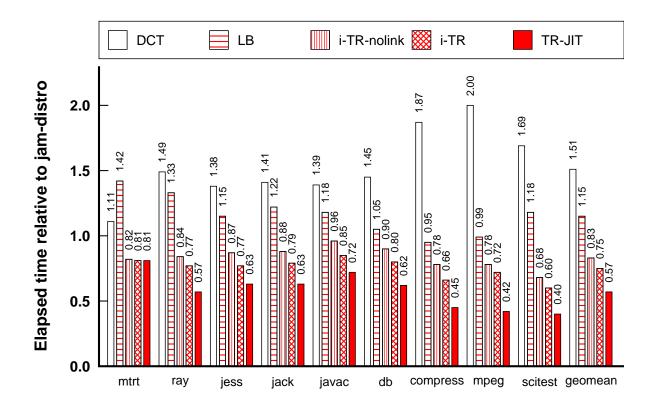

- Shows a region of the DTT during block recording mode. The body of each 6.2 block discovery dispatcher points to the corresponding virtual instruction body (Only the body for the first iload is shown). The dispatcher's payload field points to instances of instruction payload. The thread context struct is shown 88 as tcs. . . 6.3 Shows a region of the DTT just after block recording mode has finished. 89 6.4 Schematic of a trace illustrating how trace exit table (shaded) in trace payload has recorded the on-trace destination of each virtual branch ..... 93 6.5 PowerPC code for a portion of a trace region body, showing details of a trace exit and trace exit handler. This code assumes that r26 has been dedicated for the vPC. In addition the generated code in the trace exit handler uses r30, the 99 stack pointer as defined by the ABI, to store the trace exit id into the TCS. . . . Number of dispatches executed vs region shape. The y-axis has a logarithmic 7.1 scale. Numbers above bars, in scientific notation, give the number of regions dispatched. The X axis lists the SPECjvm98 benchmarks in alphabetical order. 109 7.2 Number of virtual instructions executed per dispatch for each region shape. The y-axis has a logarithmic scale. Numbers above bars are the number of virtual instructions executed per dispatch (rounded to two significant figures). SPECjvm98 benchmarks appear along X axis sorted by the average number of 7.3 Percentage trace completion rate as a proportion of the virtual instructions in a trace and code cache size for as a percentage of the virtual instructions in all Performance of each stage of Yeti enhancement from DCT interpreter to trace-7.4

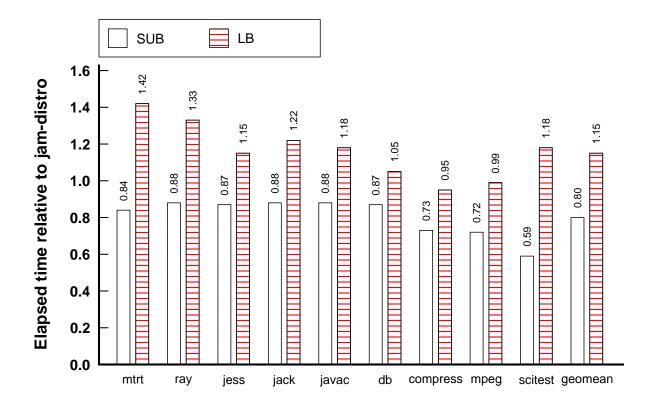

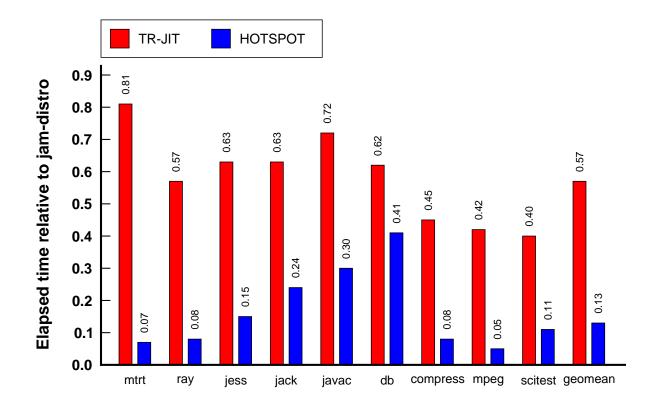

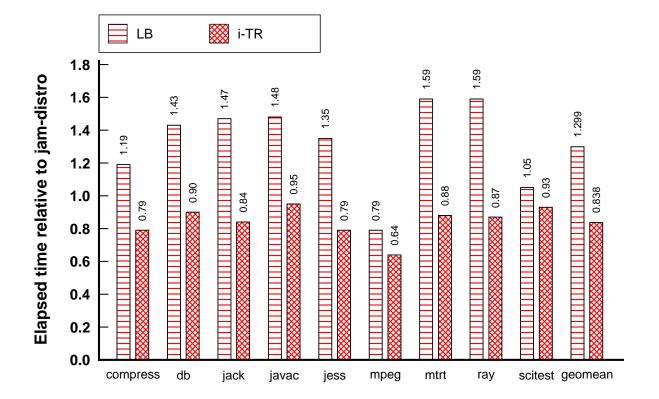

| 7.5  | Performance of Linear Blocks (LB) compared to subroutine-threaded JamVM-           |

|------|------------------------------------------------------------------------------------|

|      | 1.3.3 (SUB) relative to unmodified JamVM-1.3.3 (direct-threaded) for the SPECjvm98 |

|      | benchmarks                                                                         |

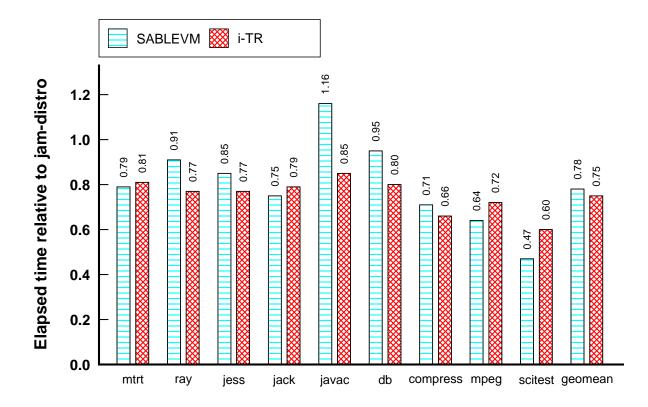

| 7.6  | Performance of JamVM interpreted traces (i-TR) and selective inlined SableVM       |

|      | 1.1.8 relative to unmodified JamVM-1.3.3 (direct-threaded) for the SPECjvm98       |

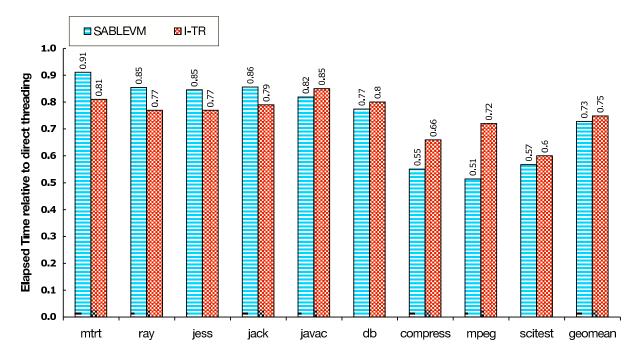

|      | benchmarks                                                                         |

| 7.7  | Performance of JamVM interpreted traces (i-TR) relative to unmodified JamVM-       |

|      | 1.3.3 (direct-threaded) and selective inlined SableVM 1.1.8 relative to direct     |

|      | threaded SableVM version 1.1.8 for the SPECjvm98 benchmarks                        |

| 7.8  | Elapsed time performance of Yeti with JIT compared to Sun Java 1.05.0_6_64         |

|      | relative to JamVM-1.3.3 (direct threading) running SPECjvm98 benchmarks 119        |

| 7.9  | Performance of Gennady Pekhimenko's Pentium port relative to unmodified            |

|      | JamVM-1.3.3 (direct-threaded) running the SPECjvm98 benchmarks 121                 |

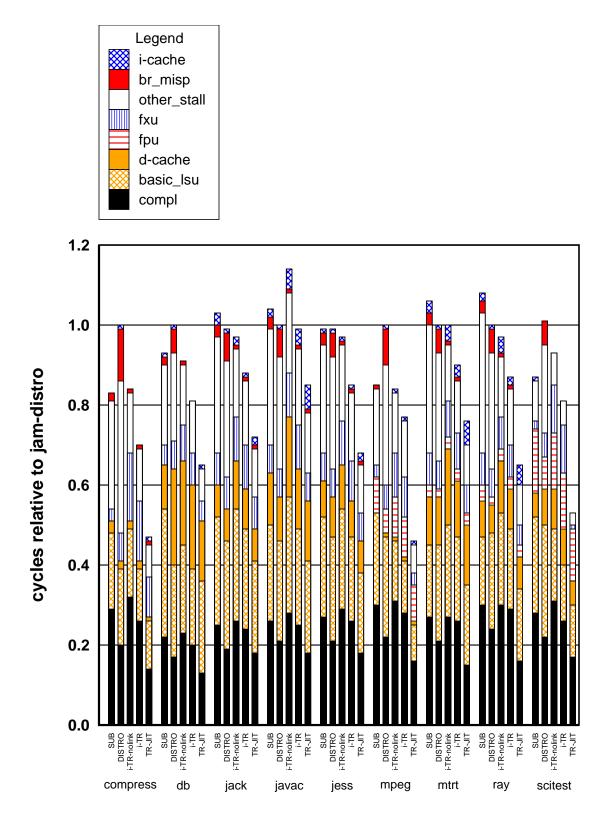

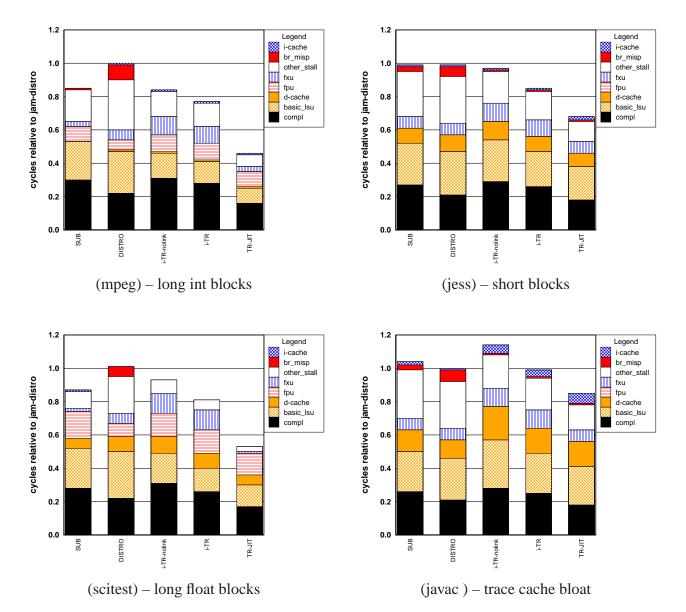

| 7.10 | Cycles relative to JamVM-1.3.3 (direct threading) running SPECjvm98 bench-         |

|      | marks                                                                              |

| 7.11 | Stall breakdown for SPECjvm98 benchmarks relative to JamVM-1.3.3 (direct           |

|      | threading)                                                                         |

## Chapter 1

## Introduction

Modern computer languages are commonly implemented in two main parts – a compiler that targets a virtual instruction set, and a so-called *high-level language virtual machine* (or simply language VM) to run the resulting virtual program. This approach simplifies the compiler by eliminating the need for any machine dependent code generation. Tailoring the virtual instruction set can further simplify the compiler by providing operations that perfectly match the functionality of the language.

There are two ways a language VM can run a virtual program. The simplest approach is to interpret the virtual program. An interpreter dispatches a *virtual instruction body* to emulate each virtual instruction in turn. A more complicated, but faster, approach deploys a dynamic, or just in time (JIT), compiler to translate the virtual instructions to machine instructions and dispatch the resulting native code. *Mixed-mode* systems interpret some parts of a virtual program and compile others. In general, compiled code will run much more quickly than virtual instructions can be interpreted. By judiciously choosing which parts of a virtual program to JIT compile, a mixed-mode system can run much more quickly than the fastest interpreter.

Currently, although many popular languages depend on virtual machines, relatively few JIT compilers have been deployed. Notable exceptions include research languages like Self and several Java Virtual Machines (JVM). Consequently, users of important computer languages,

including JavaScript, Python, and many others, do not enjoy the performance benefits of mixedmode execution.

The primary goal of our research is to make it easier to extend an interpreter with a JIT compiler. To this end we describe a new architecture for a language VM that significantly increases the performance of interpretation at the same time as it reduces the complexity of extending it to be a mixed-mode system. Our technique has two main features.

First, our JIT identifies and compiles hot interprocedural paths, or traces. Traces are single entry multiple exit regions that are easier to compile than the methods compiled by current systems. In addition, hot traces help predict the destination of virtual branches. This means that even before traces are compiled they provide a simple way to improve the interpreted performance of virtual branches.

Second, we implement virtual instruction bodies as lightweight, callable routines, and at the same time, we closely integrate the JIT compiler and interpreter. This gives JIT developers a simple alternative to compiling each virtual instruction. Either a virtual instruction is translated to native code, or instead, a call to the corresponding body is generated. The task of JIT developers is thereby simplified by making it possible to deploy a fully functional JIT compiler that compiles only a subset of virtual instructions. In addition, callable virtual instruction bodies have a beneficial effect on interpreter performance because they enable a simple interpretation technique, subroutine threading, that very efficiently executes straight-line, or non-branching, regions of a virtual program.

We prototype our ideas in Java because there exist many high-quality Java interpreters and JIT compilers with which to compare our results. We are able to determine that the performance of our prototype compares favourably with state-of-the art interpreters like JamVM and SableVM. An obvious next step would be to apply our techniques to enhance the performance of languages that currently do not offer a JIT.

The discussion in the next few sections refers to many technical terms and techniques that are described in detail in Chapter 2, which introduces the basic concepts and related work, and Chapter 3, which provides a tutorial-like description of several interpreter techniques.

## **1.1** Challenges of Method-based JIT Compilation

Today, the usual approach taken by mixed-mode systems is to identify frequently executed, or *hot*, methods. Hot methods are passed to the JIT compiler which compiles them to native code. Then, when the interpreter sees an invocation of a compiled method, it dispatches the native code instead.

**Up Front Effort** This method-oriented approach has been followed for many years, but requires a large up-front investment in effort. Such a system cannot improve the performance of a method until it can compile every feature of the language that appears in it. For significant applications this requires the JIT to compile essentially the whole language, including complicated features already implemented by high-level virtual instruction bodies, such as those for method invocation, object creation, and exception handling.

**Compiling Cold Code** Just because a method is frequently executed does not mean that all the instructions within it are frequently executed also. In fact, regions of a hot method may be *cold*, that is, they may have never executed. Compiling cold code has more implications than simply wasting compile time. Except at the very highest levels of optimization, where analyzing cold code may prove useful facts about hot regions, there is little point compiling code that never runs. A more serious issue is that cold code increases the complexity of dynamic compilation. We give three examples. First, for late binding languages such as Java, cold code likely contains references to external symbols which are not yet bound. Thus, when the cold code does eventually run, the generated code and the runtime that supports it must deal with the complexities of late binding [73]. Second, certain dynamic optimizations are not possible without runtime profiling information. Foremost amongst these is the optimization of virtual function calls. Since there is no profiling information for cold code, the JIT may have

to generate relatively slow, conservative code. This issue is even more important for runtime typed languages, like Python, in which the type of the operands of a virtual instruction may not be known until run time. Without runtime information neither a static, nor a dynamic, Python compiler may be able to determine whether the inputs of simple arithmetic operations such as addition are integers, floats, or strings. Third, as execution proceeds, some of the formerly cold regions in compiled methods may become hot. The conservative assumptions made during the initial compilation may now be a drag on performance. The straightforward-sounding approach of recompiling the method containing the formerly cold code undermines the profitability of compilation. Furthermore, it is complicated by problems such as what to do about threads that are still executing in the method or that will return to the method in the future.

### **1.2 Challenges of Efficient Interpretation**

After a virtual program is loaded by an interpreter into memory it can be executed by *dispatch-ing* each virtual instruction body (or just *body*) in the order specified by the virtual program. This is not a typical workload because the control transfer from one body to the next is data dependent on the sequence of instructions making up the virtual program. This makes the dispatch branches hard for a processor to predict. Ertl and Gregg observed that the performance of otherwise efficient interpretation is limited by pipeline stalls and flushes due to extremely poor branch prediction [28].

### **1.3 What We Need**

The challenges we identified above suggest that the architecture of a *gradually* extensible mixed-mode virtual machine should have three important properties.

1. Virtual instruction bodies should be callable. This allows JIT implementors to compile only some instructions, and fall back on the emulation functionality already implemented

by the virtual instruction bodies for others.

- 2. The unit of compilation must be dynamically determined and of flexible shape. This allows the JIT compiler to translate hot regions while avoiding cold code.

- 3. As new regions of hot code reveal themselves and are compiled, a way is needed of gracefully linking them on to previously compiled hot code.

**Callable Virtual Instruction Bodies** Packaging bodies as callable can also address the prediction problems observed in interpreters. Any straight-line sequence of virtual instructions can be translated to a very simple sequence of generated machine instructions. Corresponding to each virtual instruction we generate a single direct call which dispatches the corresponding virtual instruction body. Executing the resulting generated code thus emulates each virtual instruction in the linear sequence in turn. No branch mispredictions occur because the destination of each direct call is explicit and the return instruction ending each body is predicted perfectly by the return branch predictor present in most modern processors.

**Traces** Our system compiles frequently executed, dynamically identified interprocedural paths, or traces. Traces contain no cold code, so our system leaves all the complexities of running cold code to the interpreter. Since traces are paths through the virtual program, they explicitly predict the destination of each virtual branch. As a consequence even a very simple implementation of traces can significantly improve performance by reducing branch mispredictions caused by dispatching virtual branches. This is the basis of our new technique, *interpreted traces*.

## 1.4 Overview of Our Solution

In this dissertation we describe a system that supports dynamic compilation units of varying shapes. Just as a virtual instruction body implements a virtual instruction, a *region body*  implements a region of the virtual program. Possible region bodies include single virtual instructions, basic blocks, methods, partial methods, inlined method nests, and traces. The key idea is to package every region body as callable, regardless of the size or shape of the region of the virtual program that it implements. The interpreter can then execute the virtual program by dispatching each region body in sequence.

Region bodies corresponding to longer sequences of virtual instructions will run faster than those compiled from short ones because fewer dispatches are required. In addition, larger region bodies should offer more opportunities for optimization. However, larger region bodies are more complicated and so we expect them to require more development effort to detect and compile than short ones. This suggests that the performance of a mixed-mode VM can be gradually extended by incrementally increasing the scope of region bodies it identifies and compiles. Ultimately, the peak performance of the system should be at least as high as current method-based JIT compilers since, with basically the same engineering effort, inlined method nests could be compiled to region bodies also.

The practicality of our scheme depends on the efficiency of dispatching bodies by calling them. Thus, the first phase of our research, described in Chapters 4 and 5, was to retrofit SableVM [32], a Java virtual machine, and ocamlrun, an OCaml interpreter [14], to a new hybrid dispatch technique we call *context threading*. We evaluated context threading on PowerPC and Pentium 4 platforms by comparing branch predictor and runtime performance of common benchmarks to unmodified, direct-threaded versions of the virtual machines. We show that callable bodies can be dispatched more efficiently than dispatch techniques currently thought to be very efficient. For instance, on a Pentium 4, our subroutine threaded version of SableVM runs the SPECjym98 benchmarks about 19% faster than direct threading.

In the second phase of this research, described in Chapters 6 and 7, we gradually extended JamVM, a cleanly implemented and relatively high performance Java interpreter [53], to create Yeti (graduallY Extensible Trace Interpreter). We decided to start afresh because it proved difficult to cleanly add trace detection and profiling instrumentation to our implementation

of context threading. We chose JamVM as the starting point for Yeti, rather than SableVM, because it is simpler.

We built Yeti in five stages with the explicit intention of providing a design trajectory from a simple system to a high performance implementation. First, we repackaged all virtual instruction bodies as callable. Our initial implementation executed only single virtual instructions which were dispatched via an indirect call from a simple dispatch loop. This is slow compared to context threading but very easy to instrument. Second, we identified *linear blocks*, or sequences of virtual instructions ending in branches. Third, we extended our system to identify and dispatch *interpreted traces*, or sequences of linear blocks. Traces are significantly more complex region bodies than linear blocks because they must accommodate virtual branch instructions. Fourth, we extended our trace runtime system to link traces together. In the fifth and final stage, we implemented a naive, non-optimizing compiler to compile the traces. An interesting feature of the JIT is that it performs simple compilation and register allocation for some virtual instructions but falls back on calling virtual instruction bodies for others. Our compiler currently generates PowerPC code for about 50 integer and object virtual instructions.

We chose traces as our unit of compilation because traces have several attractive properties: (i) they can extend across the invocation and return of methods, and thus have an interprocedural view of the program, (ii) they contain only hot code, (iii) they are relatively simple to compile as they are *single-entry multiple-exit* regions of code, and (iv), it is straightforward to generate new traces and link them onto existing ones as new hot paths reveal themselves.

Instrumentation built into our prototype shows that on the average, traces accurately predict paths taken by the Java SPECjvm98 benchmark programs. This result corroborates those reported by Bala et al [8] and Duesterwald and Bala [26] for C and Fortran programs. Performance measurements show that the overhead of trace identification is reasonable. Even with our naive compiler, Yeti runs about twice as fast as unmodified JamVM.

## **1.5** Thesis Statement

The implementation of a new high-level language virtual machine should be extensible to a high performance mixed-mode system as the language matures. To achieve this, an interpreter should be designed to dispatch virtual instructions by calling them. This achieves efficient dispatch, and hence high performance interpretation, by making it easy to eliminate branch mispredictions caused by the dispatch of straight-line virtual code. Callable virtual instruction bodies also facilitate extending the interpreter with a JIT compiler because the bodies can be called from generated code. The unit of compilation translated by the JIT compiler should be a dynamically identified region containing only hot code. Hot interpretedural paths, or traces, are a good choice. Hot traces predict the destination of virtual branch instructions so they can improve the dispatch of virtual branch instructions. Traces are simple to JIT compile because they contain no cold code and no merge points. Thus, a trace-based interpreter performs better than current interpreter techniques and also is more easily extended with a JIT compiler.

## **1.6 Contributions**

We show that if virtual instruction bodies are implemented as callable routines a family of dispatch techniques becomes possible, from very simple, portable and slow, to somewhat machine dependent but much faster. Since the implementation of the virtual instruction bodies makes up a large portion of an interpreter, an attractive aspect of this approach is that there is no need to modify the bodies as more complex, and higher performing, mechanisms are implemented to dispatch them.

The simplest, and most portable, way to build an interpreter with callable bodies is to to write a dispatch loop in C that dispatches each instruction via a function pointer. This technique, called direct call threading, or DCT, performs about the same as a switch threaded interpreter. DCT is a good starting point for our family of techniques because it is simple to code and as portable as gcc. Our strategy is to extend DCT by inserting profiling code into the dispatch loop. The instrumentation dynamically identifies regions of the virtual program and translates them into callable region bodies. These region bodies can then be called from the same dispatch loop, increasing performance.

We introduce a new technique, interpreted traces, to address branch mispredictions caused by dispatch. As virtual instructions are dispatched, our profiling instrumentation uses well known heuristics to identify hot, interprocedural paths, or traces. We say the traces are interpreted because virtual instruction bodies do all the real work. Straight-line portions of each trace are implemented using subroutine threading, whereby a direct call machine instruction is generated to call the virtual instruction body implementing each virtual instruction. We follow the dispatch of each virtual branch instruction with trace exit code that exploits the fact that traces predict the destination of virtual branches. Interpreted traces require the generation of only three machine instructions: direct call, compare immediate, and conditional jump. Thus, the machine dependency of the technique is modest.

We use micro-architectural performance counter measurements to show that interpreted traces result in good branch prediction. We show that interpreted traces improve the performance of our prototype relative to direct threading about the same amount as selective inlining gains over direct threading in SableVM. This means that interpreted traces are competitive with the highest performing techniques to optimize the dispatch performance of an interpreter. We achieve this level of performance despite the fact that our system performs runtime profiling as traces are detected.

Finally, we show that interpreted traces are a good starting point for a trace-based just in time (JIT) compiler. We extend our code generator for interpreted traces such that traces may contain a mixture of compiled code for some virtual instructions and subroutine threaded dispatch for others. By compiling about 50 integer and object virtual instructions to register allocated compiled code we improve the performance of our prototype by about 30% over interpreted traces to run about twice as fast as the direct threaded system with which we started.

Taken together, direct call threading, interpreted traces, and our trace-based JIT provide a

design trajectory for a language VM with a range of performance from switch threading, a very widely deployed entry level technique, to about double the performance of a direct threaded interpreter. The fact that interpreted traces are gradually extensible in this way makes them a good strategic design option for future language virtual machines.

#### **Summary of Contributions**

- If virtual instruction bodies are implemented as callable routines straight-line sections of virtual programs can be efficiently interpreted by load-time generated sequences of subroutine threaded code. We show that on modern processors the extra path length of the call and return instructions used by subroutine threading is more than made up for by the elimination of stalls caused by mispredicted indirect branches used by direct threading.

- 2. We introduce a new technique, interpreted traces, which identifies traces, or hot paths, to predict the destination of virtual branch instructions. We implement interpreted traces in JamVM, a high performance Java interpreter, and show that they outperform direct threading by 25%. This is about the same speedup achieved by SableVM's implementation of selective inlining.

- 3. The code generator for interpreted traces can be gradually extended to be a trace-based JIT by adding support for virtual instructions one at a time. Traces are simple to compile as they contain no cold code or merge points. Our trace-based JIT currently compiles about 50 virtual instructions and obtains a speed up of about 30% over interpreted traces.

## **1.7 Outline of Thesis**

We describe an architecture for a virtual machine interpreter that facilitates the gradual extension to a trace-based mixed-mode JIT compiler. We demonstrate the feasibility of this approach in a prototype, Yeti, and show that performance can be gradually improved as larger program regions are identified and compiled.

In Chapters 2 and 3 we present background and related work on interpreters and JIT compilers. In Chapter 4 we describe the design and implementation of context threading. Chapter 5 describes how we evaluated context threading. The design and implementation of Yeti is described in Chapter 6. We evaluate the benefits of this approach in Chapter 7. Finally, we discuss possible avenues for future work and conclude in Chapter 8.

## Chapter 2

## Background

Researchers have investigated how virtual machines should execute high-level language programs for many years. The research has been focused on a few main areas. First, innovative virtual machine support can play a role in the deployment of qualitatively new and different computer languages. Second, virtual machines provide an infrastructure by which ordinary computer languages can be more easily deployed on many different hardware platforms. Third, researchers continually devise new ways to enable language VMs to run virtual programs faster.

This chapter will describe research which touches on all these issues. We will briefly discuss interpretation in preparation for a more in-depth treatment in Chapter 3. We will describe how modern object-oriented languages depend on the virtual machine to efficiently invoke methods by following the evolution of this support from the early efforts to modern speculative inlining techniques. Finally, we will briefly describe trace-based binary optimization to set the scene for Chapter 6.

## 2.1 High Level Language Virtual Machine

A static compiler is probably the best solution when performance is paramount, portability is not a great concern, destinations of calls are known at compile time and programs bind to external symbols before running. Thus, most third generation languages like C and FORTRAN are implemented this way. However, if the language is object-oriented, binds to external references late, and must run on many platforms, it may be advantageous to implement a compiler that targets a fictitious *high-level language virtual machine* (HLL VM) instead.

In Smith's taxonomy, an HLL VM is a system that provides a process with an execution environment that does not correspond to any particular hardware platform [65]. The interface offered to the high-level language application process is usually designed to hide differences between the platforms to which the VM will eventually be ported. For instance, UCSD Pascal p-code [17] and Java bytecode [52] both express virtual instructions as stack operations that take no register arguments. Gosling, one of the designers of the Java virtual machine, has said that he based the design of the JVM on the p-code machine [3]. Smalltalk [36], Self [74] and many other systems have taken a similar approach. This makes it easier to port the VM between hardware platforms that have variously sized register files. A VM may also provide virtual instructions that support peculiar or challenging features of the language. For instance, a Java virtual machine has specialized virtual instructions (eg. invokevirtual) in support of virtual method invocation. This allows the compiler to generate a single, relatively high-level virtual instruction instead of a sequence of complex machine and ABI dependent instructions.

This approach has benefits for the users as well. For instance, applications can be distributed in a platform neutral format. In the case of the Java class libraries or UCSD Pascal programs, the amount of virtual software far exceeds the size of the VM. The advantage is that the relatively small amount of effort required to port the VM to a new platform enables a large body of virtual applications to run on the new platform also.

There are various approaches a HLL VM can take to actually execute a virtual program. An interpreter fetches, decodes, then emulates each virtual instruction in turn. Hence, interpreters are slow but can be very portable. Faster, but less portable, a dynamic compiler can translate to native code and dispatch regions of the virtual application. A dynamic compiler can exploit runtime knowledge of program values so it can sometimes do a better job of optimizing the program than a static compiler [68].

#### Java Source Java Bytecode int f(){ int a,b,c; ... c = a + b + 1; ... } Java Bytecode int f(boolean); iload a iload b iconst 1 iadd iadd istore c

Figure 2.1: Example Java Virtual Program showing source (on the left) and Java virtual instructions, or bytecodes, on the right.

#### 2.1.1 Overview of a Virtual Program

A virtual program, as shown in Figure 2.1, is a sequence of virtual instructions and related meta-data. The figure introduces an example program we will use as a running example, so we will briefly describe it here. First, a compiler, javac in the example, creates a *class file* describing the virtual program in a standardized format. (We show only one method, but any real Java example would define a whole class.) Our example consists of just one Java expression  $\{c=a+b+1\}$  which adds the values of two Java local variables and a constant and stores the result in a third. The compiler has translated this to the sequence of virtual instructions shown on the right. The actual semantics of the virtual instructions are not important to our example other than to note that none are virtual branch instructions.

The distinction between a virtual instruction and an *instance* of a virtual instruction is conceptually simple but sometimes hard to clearly distinguish in prose. We will always refer to a specific use of a virtual instruction as an "instance". For example, the first instruction in our example program is an instance of iload. On the other hand, we might also use the term virtual instruction to refer to a kind of operation, for example that the iload virtual instruction takes one parameter.

Java virtual instructions may take implicit arguments that are passed on a expression stack. For instance, in Figure 2.1, the iadd instruction pops the top two slots of the expression stack and pushes their sum. This style of instruction set is very compact because there is no need to explicitly list parameters of most virtual instructions. Consequently many virtual instructions, like iadd, consist of only the opcode. Since there are fewer than 256 Java virtual instructions, the opcode fits in a byte, and so Java virtual instructions are often referred to as *bytecode*.

In addition to arguments passed implicitly on the stack, certain virtual instructions take immediate operands. In our example, the iconst virtual instruction takes an immediate operand of 1. Immediate operands are also required by virtual branch instructions (the offset of the destination) and by various instructions used to access data.

The bytecode in the figure depends on a stack frame organization that distinguishes between local variables and the expression stack. *Local variable array* slots, or *lva* slots, are used to store local variables and parameters. The simple function shown in the figure needs only four local variable slots. The first slot, lva[0], stores a hidden parameter, the object handle<sup>1</sup> to the invoked-upon object and is not used in this example. Subsequent slots, lva[1], lva[2] and lva[3] store a, b and c respectively. The expression stack is used to store temporaries for most calculations and parameter passing. In general "load" form bytecodes push values in lva slots onto the expression stack. Bytecodes with "store" in their mnemonic typically pop the value on top of the expression stack and store it in a named lva slot.

#### 2.1.2 Interpretation

An interpreter is the simplest way for an HLL VM to execute a guest virtual program. Whereas the persistent format of a virtual program conforms to some external specification, when it is read by an interpreter the structure of its *loaded representation* is chosen by the designers of the interpreter. For instance, designers may prefer a representation that word-aligns all immediate parameters regardless of their size. This would be less compact, but more portable and potentially faster to access, than the original byte code on most architectures.

An abstraction implemented by most interpreters is the notion of a virtual program counter,

<sup>&</sup>lt;sup>1</sup>lva[0] stores the local variable known as this to Java (and C++) programmers.

or vPC. It points into the loaded representation of the program and serves two main purposes. First, the vPC is used by dispatch code to indicate where in the virtual program execution has reached and hence which virtual instruction to emulate next. Second, the vPC is conventionally referred to by virtual instruction bodies to access immediate operands.

#### Interpretation is not efficient

We do not expect interpretation to be efficient compared to executing compiled native code. Consider Java's iadd virtual instruction. On a typical processor an integer add can be performed in one instruction. To emulate a virtual addition instruction requires three or more additional instructions to load the inputs from and store the result to the expression stack.

However, it is not just the path length of emulation that causes performance problems. Also important is the latency of the branch instructions used to transfer control to the virtual instruction body. To optimize dispatch. researchers have proposed various *dispatch* techniques to efficiently branch from body to body. Recently, Ertl and Gregg showed that on modern processors branch mispredictions caused by dispatch branches are a serious drain on performance [28, 29].

When emulated by most current high-level language virtual machines, the branching patterns of the virtual program are hidden from the branch prediction resources of the underlying real processor. This is despite the fact that a typical virtual machine defines roughly the same sorts of branch instructions as does a real processor and that a running virtual program exhibits similar patterns of virtual branch behaviour as does a native program running on a real CPU. In Section 3.5 we discuss in detail how our approach to dispatch deals with this issue, which we have dubbed the *context problem*.

#### **2.1.3 Early Just in Time Compilers**

A faster way of executing a guest virtual program is to compile its virtual instructions to native code before it is executed. This approach long predates Java, perhaps first appearing for APL

on the HP3000 [48] as early as 1979. Deutsch and Schiffman built a just in time (JIT) compiler for Smalltalk in the early 1980's that ran about twice as fast as interpretation [24].

Early systems were highly memory constrained by modern standards. It was of great concern, therefore, when translated native code was found to be about four times larger than the originating bytecode<sup>2</sup>. Lacking virtual memory, Deutsch and Schiffman took the view that dynamic translation of bytecode was a space time trade-off. If space was tight then native code (space) could be released at the expense of re-translation (time). Nevertheless, their approach was to execute only native code. Each method had to be fetched from a native code cache or else re-translated before execution. Today a similar attitude prevails except that it has also been recognized that some code is so infrequently executed that it need not be translated in the first place. The bytecode of methods that are not hot can simply be interpreted.

A JIT can improve the performance of a JVM substantially. Relatively early Java JIT compilers from Sum Microsystems, as reported by the development team in 1997, improved the performance of the Java raytrace application by a factor of 2.2 and compress by 6.8 [19]<sup>3</sup>. More recent JIT compilers have increased the performance further [2, 4, 70]. For instance, on a modern personal computer Sun's Hotspot server dynamic compiler currently runs the entire SPECjvm98 suite more than 4 times faster than the fastest interpreter. Some experts suggest that in the not too distant future, systems based on dynamic compilers will run *faster* than the code generated by static compilers [68, 67].

## 2.2 Challenges to HLL VM Performance

Modern languages offer users powerful features that challenge VM implementors. In this section we will discuss the impact of object-oriented method invocation and late binding of ex-

<sup>&</sup>lt;sup>2</sup>This is less than one might fear given that on a RISC machine one typical arithmetic bytecode will be naïvely translated into two loads (pops) from the expression stack, one register-to-register arithmetic instruction to do the real work and a store (push) back to the new top of the expression stack.

<sup>&</sup>lt;sup>3</sup>These benchmarks are singled out because they eventually were adopted by the SPEC consortium to be part of the SPECjvm98 [66] benchmark suite.

ternal references. There are many other issues that affect Java performance which we discuss only briefly. The most important amongst them are memory management and thread synchronization.

*Garbage collection* refers to a set of techniques used to manage memory in Java (as in Smalltalk and Self) where unused memory (garbage) is detected automatically by the system. As a result, the programmer is relieved of any responsibility for freeing memory that he or she has allocated. Garbage collection techniques are somewhat independent of dynamic compilation techniques. The primary interaction requires that threads can be stopped in a well-defined state prior to garbage collection. So-called *safe points* must be defined at which a thread periodically saves its state to memory. Code generated by a JIT compiler must ensure that safe points occur frequently enough that garbage collection is not unduly delayed. Typically this means that each transit of a loop must contain at least one safe point.

Java provides explicit, built-in, support for threads. *Thread synchronization* refers mostly to the functionality that allows only one thread to enter certain regions of code at a time. Thread synchronization must be implemented at various points and the techniques for implementing it must be supported by code generated by the JIT compiler.

## 2.2.1 Polymorphism and the Implications of Object-oriented Programming

Over the last few decades, object-oriented development grew from a vision, to an industry trend, to a standard programming tool. Object-oriented techniques stressed development systems in many ways, but the one we need to examine in detail here is the challenge of polymorphic method invocation.

The destination of a callsite in an object-oriented language is not determined solely by the signature of a method, as in C or FORTRAN. Instead, it is determined at run time by a combination of the method signature and the class of the invoked-upon object. Callsites are said to be *polymorphic* as the invoked-upon object may turn out to be one of potentially many

```

void sample(Object[] otab){

for(int i=0; i<otab.length; i++){

otab[i].toString(); //polymorphic callsite

}

}</pre>

```

Figure 2.2: Example of Java method containing a polymorphic callsite

classes.

Most object-oriented languages categorize objects into a hierarchy of *classes*. Each object is an *instance* of a class which means that the methods and data fields defined by that class are available for the object. Each class, except the root class, has a *super-class* or *base-class* from which it *inherits* fields and methods.

Each class may override a method and so at run time the system must dispatch the definition of the method corresponding to the class of the invoked-upon object. In many cases it is not possible to deduce the exact type of the object at compile time.

A simple example will make the above description concrete. When it is time to debug a program almost all programmers rely on facilities to view a textual description of their data. In an object-oriented environment this suggests that each object should define a method that returns a string description of itself. This need was recognized by the designers of Java and consequently they defined a method in the root class Object:

public String toString()

to serve this purpose. The toString<sup>4</sup> method can be invoked on every Java object. Consider an array of objects in Java. Suppose we code a loop that iterates over the array and invokes the toString method on each element as in Figure 2.2.

There are literally hundreds of definitions of toString in a Java system and in many cases the compiler cannot discern which one will be the destination of the callsite. Since it is not possible to determine the destination of the callsite at compile time, it must be done

<sup>&</sup>lt;sup>4</sup>It is the text returned by toString that appears in various views of an interactive debugger

when the program executes. Determining the destination taxes performance in two main ways. First, locating the method to dispatch at run time requires computation. This will be discussed in Section 2.4.1. Second, the inability to predict the destination of a callsite at compile time reduces the efficacy of interprocedural optimizations and thus results in relatively slow systems. This is discussed next.

#### **Impact of Polymorphism on Optimization**

Optimization can be stymied by polymorphic callsites. At compile time, an optimizer cannot determine the destination of a call, so obviously the target cannot be inlined. In fact, standard interprocedural optimization as carried out by an optimizing C or FORTRAN compiler is simply not possible [55].

In the absence of interprocedural information, an optimizer cannot guess what calculations are made by a polymorphic callee. Knowledge of the destination of the callsite would permit a more precise analysis of the values modified by the call. For instance, with runtime information, the optimizer may know that only one specific version of the method exists and that this definition simply returns a constant value. Code compiled speculatively under the assumption that the callsite remains monomorphic could constant propagate the return value forward and hence be much better than code compiled under the conservative assumption that other definitions of the method may be called.

Given the tendency of modern object-oriented software to be factored into many small methods which are called throughout a program, even in its innermost loops, these optimization barriers can significantly degrade the performance of the generated code. A typical example might be that common subexpression elimination cannot combine identical memory accesses separated by a polymorphic callsite because it cannot prove that all possible callees do not kill the memory location. To achieve performance comparable to procedural compiled languages, interprocedural optimization techniques must somehow be applied to regions laced with polymorphic callsites. Section 2.4 describes various solutions to these issues.

### 2.2.2 Late binding

A basic design issue for any language is when external references are resolved. Java binds references very late in order to support flexible packaging in general and downloadable code in particular. (This contrasts with traditional languages like C, which rely on a link-editor to bind to external symbols before they run.) The general idea is that a Java program may start running before all the classes that it needs are locally available. In Java, binding is postponed until the last possible moment, when the virtual instruction making the reference executes for the first time. Then, during the first execution, the reference is either resolved or a software exception is raised. This means that the references a program attempts to resolve depends on the path of execution through the code.

This approach is convenient for users and challenging for language implementors. Whenever Java code is executed for the first time the system must be prepared to handle unresolved external references. An obvious, but slow, approach is to simply check whether an external reference is resolved each time the virtual instruction executes. For good performance, only the first execution should be burdened with any binding overhead. One way to achieve this is for the virtual program to rewrite itself when an external reference is resolved. For instance, suppose a virtual instruction, vop, takes an immediate parameter that names an unresolved class or method. When the virtual instruction is first executed the external name is resolved and an internal VM data structure describing it is created. The loaded representation of the virtual instruction is then rewritten, say to vop\_resolved, which takes the address of the data structure as an immediate parameter. The implementation of vop\_resolved can safely assume that the external reference has been resolved successfully. Subsequently vop\_resolved will execute in place of vop with no binding overhead<sup>5</sup>.

The process of virtual instruction rewriting is relatively simple to carry out when instruc-

<sup>&</sup>lt;sup>5</sup>This roughly describes how JamVM and SableVM handle late binding.

tions are being interpreted. For instance, it is possible to fall back on standard thread support libraries to protect overwriting from multiple threads racing to rewrite the instruction. It is more challenging if the resolution is being carried out by dynamically compiled native code [73].

# 2.3 Early Dynamic Optimization

Early efforts to build dynamic optimizers were embedded in applications or C or FORTRAN run time systems.

### 2.3.1 Manual Dynamic Optimization

Early experiments with dynamic optimization indicated that large performance improvements are possible. Typical early systems were application-specific. Rather than compile a language, they dynamically generated machine code to calculate the solution to a problem described by application specific data. Later, researchers built semi-automatic dynamic systems that would re-optimize regions of C programs at run time [51, 5, 34, 38, 37].

Although the semi-automatic systems did not enable dramatic performance improvements across the board, this may be a consequence of the performance baseline to which they compared themselves. The prevalent programming languages of the time were supported by static compilation and so it was natural to use the performance of highly optimized binaries as the baseline. The situation for modern languages like Java is somewhat different. Dynamic techniques that do not pay off relative to statically optimized C code may be beneficial when applied to code naïvely generated by a JIT. Consequently, a short description of a few early systems seems worthwhile.

### 2.3.2 Application specific dynamic compilation

In 1968 Ken Thompson built a dynamic compiler which accepted a textual description of a regular expression and dynamically translated it into machine code for an IBM 7094 computer

[49]. The resulting code was dispatched to find matches quickly.

In 1985 Pike et al. invented an often-cited technique to generate good code for quickly copying, or bitblt'ing, regions of pixels from memory onto a display [57]. They observed that there was a bewildering number of special cases (caused by various alignments of pixels in display memory) to consider when writing a good general purpose bitblit routine. Instead they wrote a dynamic code generator that could produce a good (near optimal) set of machine instructions for each special case. At worst, their system executed only about 400 instructions to generate code for a bitblit.

### 2.3.3 Dynamic Compilation of Manually Identified Static Regions

In the mid-1990's Lee and Leone [51] built FABIUS, a dynamic optimization system for the research language ML [34]. FABIUS depends on a particular use of *curried functions*. Curried functions take one or more functions as parameters and return a new function that is a composition of the parameters. FABIUS interprets the call of a function returned by a curried function as a clue from the programmer that dynamic re-optimization should be carried out. Their results, which they describe as preliminary, indicate that small, special purpose, applications such as sparse matrix multiply or a network packet filter may benefit from their technique but the time and memory costs of re-optimization are difficult to recoup in general purpose code.

More recently it has been suggested that C and FORTRAN programs can benefit from dynamic optimization. Auslander et al [5], Grant et al [38, 37] and others have built semi-automatic systems to investigate this. Initially these systems required the user to identify regions of the program that should be dynamically re-optimized as well as the variables that are runtime constant. Later systems allowed the user to identify only the program variables that are runtime constants and could automatically identify which regions should be re-optimized at run time.

In either case, the general idea is that the user indicates regions of the program that may

be beneficial to dynamically compile at run time. The dynamic region is precompiled into template code. Then, at run time, the values of runtime constants can be substituted into the template and the dynamic region re-optimized. Auslander's system worked only on relatively small kernels like matrix multiply and quicksort. A good way to look at the results was in terms of *break even point*. In this view, the kernels reported by Auslander had to execute from about one thousand to a few tens of thousand of times before the improvement in execution time obtained by the dynamic optimization outweighed the time spent re-compiling and re-optimizing.

Subsequent work by Grant et al. created the DyC system [38, 37]. DyC simplified the process of identifying regions and applied more elaborate optimizations at run time. This system can handle real programs, although even the streamlined process of manually designating only runtime constants is reported to be time consuming. Their methodology allowed them to evaluate the impact of different optimizations independently, including complete loop unrolling, dynamic zero and copy propagation, dynamic reduction of strength and dynamic dead assignment elimination to name a few. Their results showed that only loop unrolling had sufficient impact to speed up real programs and in fact without loop unrolling there would have been no overall speedup at all.

# 2.4 Dynamic Object-oriented optimization

Some of the challenges to performance discussed above are caused by new, more dynamic language features. Consequently, optimizations that have traditionally been carried out at compile time are no longer effective and must be redeployed as dynamic optimizations carried out at run time. The best example, polymorphic method invocation, will be discussed next.

### 2.4.1 Finding the destination of a polymorphic callsite

Locating the definition of a method for a given object at run time is a search problem. To search for a method definition corresponding to a given object the system must search the classes in the hierarchy. The search starts at the class of the object, proceeds to its super class, to the super class of its super class, and so on, until the root of the class hierarchy is reached. If each method invocation requires the search to be repeated, the process will be a significant tax on overall performance. Nevertheless, this is exactly what occurs in a naïve implementation of Smalltalk, Self , Java, JavaScript or Python.

If the language permits early binding, the search may be converted to a table lookup at compile-time. For instance, in C++, all the possible destinations of a callsite are known when the program is loaded. As a result, a C++ virtual callsite can be implemented as an indirect branch via a virtual table specific to the class of the object invoked on. This reduces the cost to little more than a function pointer call in C. The construction and performance of virtual function tables has been heavily studied, for instance by Driesen [25].

Real programs tend to have low *effective polymorphism*. This means that the average callsite has very few actual destinations. If fact, most callsites are *effectively monomorphic*, meaning they always call the same method. Note that low effective polymorphism does not imply that a smart compiler should have been able to deduce the destination of the call. Rather, it is a statistical observation that real programs typically make less use of polymorphism than they might.

### **Inlined Caching and Polymorphic Inlined Caching**

For late-binding languages it is seldom possible to generate efficient code for a callsite at compile time. In response, various researchers have investigated how it might be done at run time. In general, it pays to cache the destination of a callsite when the callsite is commonly executed and its effective polymorphism is low. The *in-line cache*, invented by Deutsch and Schiffman [24] for Smalltalk more than 20 years ago, replaces the polymorphic callsite with

the native instruction to call the cached method. The prologue of all methods is extended with fix-up code in case the cached destination is not correct. Deutsch and Shiffman reported hitting the in-line cache about 95% of the time for a set of Smalltalk programs.

Hölzle [43] extended the in-line cache to be a *polymorphic in-line cache* (PIC) by generating code that successively compares the class of the invoked object to a few possible destination types. The implementation is more difficult than an in-line cache because the dynamically generated native code sequence must sequentially compare and conditionally branch against several possible destinations. A PIC extends the performance benefits of an in-line cache to effectively polymorphic callsites. For example, on a SPARCstation-2 Hölzle's lookup would cost only 8 + 2n cycles, where n is the actual polymorphism of the callsite. A PIC lookup costs little more than an in-line cache for effectively monomorphic callsites and is much faster for callsites that are effectively polymorphic.

### 2.4.2 Smalltalk and Self

Smalltalk adopted the position that essentially every software entity should be represented as an object. A fascinating discussion of the qualitative benefits anticipated from this approach appears in Goldberg's book [35].

The designers of Self took an even more extreme position. They held that even control flow should be expressed using object-oriented concepts<sup>6</sup>. They understood that this approach would require them to invent new ways to efficiently optimize message invocation if the performance of their system was to be reasonable. Their research program was extremely ambitious and they explicitly compared the performance of their system to optimized C code executing the same algorithms.

In addition, the Self system aimed to support the most interactive programming environment possible. Self supports debugging, editing and recompiling methods while a program